US 20120127065A1

### (19) United States

# (12) Patent Application Publication

Koyama et al.

### (10) Pub. No.: US 2012/0127065 A1

(43) **Pub. Date:** May 24, 2012

## (54) **DISPLAY DEVICE AND METHOD OF DRIVING THE SAME**

(75) Inventors: **Jun Koyama**, Kanagawa (JP);

Hajime Kimura, Kanagawa (JP)

(73) Assignee: Semiconductor Energy

Laboratory Co., Ltd.

(21) Appl. No.: 13/300,867

(22) Filed: Nov. 21, 2011

#### Related U.S. Application Data

(63) Continuation of application No. 11/836,275, filed on Aug. 9, 2007, now Pat. No. 8,063,895, which is a continuation of application No. 10/785,809, filed on Feb. 24, 2004, now Pat. No. 7,262,749, which is a continuation of application No. 10/040,084, filed on Oct. 26, 2001, now Pat. No. 6,697,057.

#### (30) Foreign Application Priority Data

Oct. 27, 2000 (JP) ...... 2000-328751

#### **Publication Classification**

(51) Int. Cl. *G09G 3/30*

(2006.01)

(52) US CL

(57) **ABSTRACT**

Disclosed is an EL display device by which accurate gray scales can be obtained. The EL display device comprises a source signal line driving circuit which includes an operation amplifier electrically connected to a correction TFT and a source signal line, and a pixel which includes an EL element and a driving TFT. An inputted analog signal voltage is converted into a current, the current is converted into a gate-source voltage of the correction TFT that has the same polarity as the driving TFT, the gate-source voltage is supplied as a source line signal to the source signal line, and the source line signal is applied to a gate electrode of the driving TFT. Thus the EL element can emit light at a luminance linearly corresponding to the inputted analog signal voltage.

Fig. 2

Fig. 4

Fig. 5 (Prior Art)

Fig. 8

Fig. 18E

2501

2504

## DISPLAY DEVICE AND METHOD OF DRIVING THE SAME

#### BACKGROUND OF THE INVENTION

[0001] 1. Field of the Invention

[0002] The present invention relates to an active matrix EL display device in which each pixel has TFTs (thin film transistors) and an EL element. Specifically, the invention relates to an active matrix EL display device of analog gray scale system in which gray scales are reflection of analog changes in amount of current flowing into EL elements.

[0003] In this specification, EL elements include those emit light from singlet excitation (fluorescence) and those emit light from triplet excitation (phosphorescence) both.

[0004] 2. Description of the Related Art

[0005] With recent flood of data communication, demands for data communication equipment are increasing. In data communication equipment, display devices for displaying images are indispensable. The display devices that are attracting attention are EL display devices using an EL element that is a self-luminous element.

[0006] As display units larger in size and higher in definition are needed in data communication equipment, active matrix display devices in which each pixel has TFTs are becoming the main stream display devices.

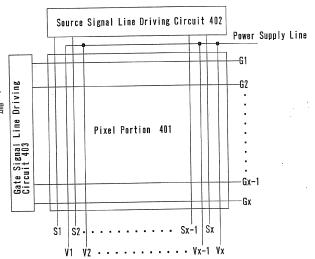

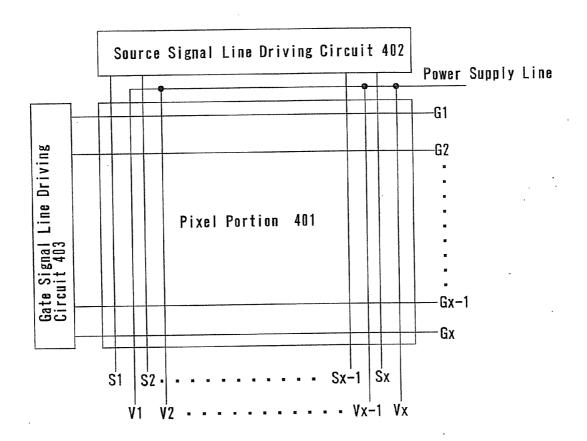

[0007] FIG. 4 is a block diagram of an active matrix EL display device. A source signal line driving circuit 402 and a gate signal line driving circuit 403 are arranged in the periphery of a pixel portion 401. A signal outputted from the source signal line driving circuit 402 is inputted to source signal lines S1 to Sx to be sent to pixels. A signal outputted from the gate signal line driving circuit 403 is inputted to gate signal lines G1 to Gy to be sent to pixels. Power supply lines (power lines) V1 to Vx are arranged in parallel to the source signal lines to supply current to pixels.

**[0008]** As one way to reduce the size of a display device as well as manufacture cost, sometimes a pixel portion and a driving circuit portion (composed of a source signal line driving circuit and a gate signal line driving circuit) are formed on the same substrate. In this case, a polycrystalline semiconductor film is used to form TFTs that constitute the pixel portion and the driving circuit portion.

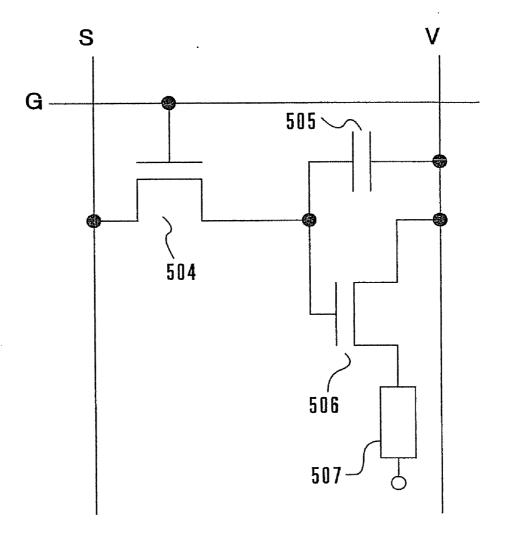

[0009] This can be applied to the active matrix EL display device of FIG. 4, and an example of the pixel structure thereof is shown in FIG. 5.

[0010] A switching TFT 504 has a gate electrode connected to a gate signal line G that is one of the gate signal lines G1 to Gy. The switching TFT also has a source region and a drain region one of which is connected to a source signal line S that is one of the source signal lines S1 to Sx and the other of which is connected to one of gate electrodes of a capacitor 505 and to a gate electrode of an EL driving TFT 506. Of two electrodes of the capacitor 505, one that is not connected to the switching TFT 504 is connected to a power supply line V that is one of the power supply lines V1 to Vx. The EL driving TFT 506 has a source region and a drain region one of which is connected to the power supply line V and the other of which is connected to an EL element 507.

[0011] In a pixel whose gate signal line G is selected, the signal electric potential of the source signal line S is inputted to one of the electrodes of the capacitor 505 through the switching TFT 504 that has been turned conductive. The voltage between the electrodes of the capacitor 505 is applied to the gate electrode of the EL driving TFT 506. In accordance

with this voltage applied, a current flows from the power supply line V through the EL driving TFT **506** into the EL element **507** and causes the EL element **507** to emit light.

[0012] The luminance of light emitted from the EL element 507 is almost in proportion with the amount of current flowing into the EL element 507. Therefore gray scales are obtained by changing the amount of current flowing into the EL element 507.

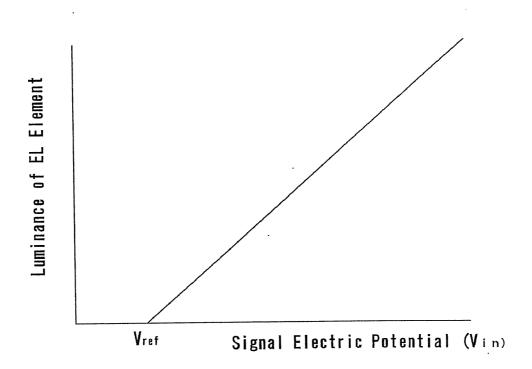

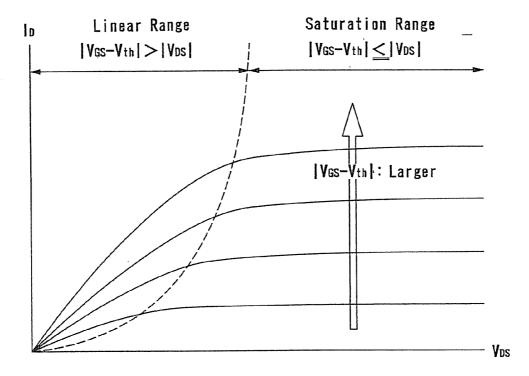

[0013] In the display device shown in FIG. 5, the current flowing into the EL element 507 is inputted from the power supply line V through the EL driving 506. The relation between a drain-source voltage  $V_{DS}$  of a TFT and a drain current  $I_D$  of the TFT in general is as shown in FIG. 8.

[0014] FIG. 8 is a graph showing plural  $I_D$  curves obtained by varying the value of a gate voltage  $V_{GS}$ . The drain current  $I_D$  becomes larger as the absolute value of the difference between the gate voltage  $V_{GS}$  and a threshold voltage  $V_{th}$  of the EL driving TFT 506 ( $|V_{GS}-V_{th}|$ ) becomes larger, in other words, as the absolute value  $|V_{GS}|$  of the gate voltage  $V_{GS}$  becomes larger.

[0015] When the absolute value  $|V_{GS}-V_{th}|$  of the difference between the gate voltage  $V_{GS}$  and the threshold voltage  $V_{th}$  of the EL driving TFT 506 is larger than the absolute value  $|V_{DS}|$  of the drain-source voltage  $V_{DS}$ , the TFT operates in a linear range. On the other hand, the TFT operates in a saturation range when  $|V_{GS}-V_{th}|$  is equal to or smaller than the absolute value  $|V_{DS}|$  (of the drain-source voltage  $V_{DS}$ .

[0016] The EL driving TFT 506 generally operates in the saturation range where the absolute value  $|V_{DS}|$  (of the drainsource voltage  $V_{DS}$  is equal to or greater than the absolute value  $|V_{GS}-V_{th}|$  of the difference between the gate voltage  $V_{GS}$  and the threshold voltage  $V_{th}$  of the EL driving TFT 506. [0017] In the saturation range, the drain current  $I_D$  of the TFT is in proportion to the second power of the gate voltage  $V_{GS}$  as shown in the following Equation 1.

$$I(\frac{1}{2})\mu_0 C_0(W^2/L^2)(V_{GS}-V_{th})^2$$

(Equation 1)

wherein,  $V_{\it th}$  represents the threshold voltage,  $\mu_0$  represents the effective mobility,  $C_0$  represents the capacitance of a gate insulating film per unit area, W represents the gate width, and L represents the gate length.

[0018] In accordance with this equation, the electric potential to be inputted to the source signal line S is changed such that the TFT receives a gate voltage in proportion to the square root of the desired amount current to be inputted to the EL element 507. In this way, the EL element is caused to emit light of desired luminance.

[0019] When an image is to be displayed, an electric potential according to a desired gray scale is calculated by Equation 1 and is inputted to the source signal line.

[0020] However, a video signal inputted from the external generally has an analog electric potential that changes linearly with respect to the luminance obtained. Therefore accurate gray scales cannot be obtained when a video signal supplied from the external is inputted to the signal line as it is.

**[0021]** There is a countermeasure in which an external correction circuit converts the video signal into a drive signal in advance to suit the characteristics of the EL driving TFT and then the signal is sampled by the source signal line driving circuit and outputted to pixels to obtain a given gray scale.

[0022] This measure, however, complicates the operation since it requires video signal processing as above before the signal is inputted to the source signal line driving circuit. Furthermore, the measure needs the correction circuit in addi-

tion to the source signal line driving circuit to obstruct reduction in size of the display device.

[0023] Accordingly, a method has to be found which makes it possible to obtain a given gray scale when a video signal is inputted directly to the source signal line driving circuit.

#### SUMMARY OF THE INVENTION

[0024] The present invention has been made in view of the above, and an object of the present invention is therefore to provide a display device having a source signal line driving circuit that makes a current flowing through an EL element of a pixel portion linearly correspond to a video signal inputted from the external and then sampled.

[0025] A given gray scale thus can readily be obtained when a video signal is inputted directly.

[0026] The structure of the present invention will be shown below.

[0027] According to the present invention, there is provided a display device having in each pixel an EL element, a source signal line, and a driving TFT for driving the EL element, the device characterized by comprising:

[0028] means for converting an inputted analog signal voltage into a current;

[0029] means for converting the current into a gate-source voltage of a TFT that has the same polarity as the driving TFT; [0030] means for supplying the gate-source voltage as a source line signal to the source signal line; and

[0031] means for supplying the source line signal to a gate electrode of the driving TFT, and converting the source line signal into a current in the driving TFT to drive the EL element.

[0032] According to the present invention, there is provided a display device having in each pixel a source signal line, an EL driving TFT, a power supply line, and an EL element, the source signal line inputting its signal voltage to a gate electrode of the EL driving TFT, the power supply line supplying a current to the EL element through the source-drain of the EL driving TFT, the device characterized in that:

[0033] —a correction TFT having the same polarity as the EL driving TFT is provided;

[0034] an analog signal voltage sampled is converted into a signal current linearly corresponding thereto;

[0035] the signal current flows into the source-drain of the correction TFT to output, to the source signal line, a drive voltage obtained by adding the gate-source voltage of the correction TFT to a reference electric potential; and

[0036] the gate-source voltage of the EL driving TFT is substantially equal to the gate-source voltage of the correction TFT when the electric potential of the power supply line is set as the reference electric potential.

[0037] According to the present invention, there is provided a display device having in each pixel a source signal line, an EL driving TFT, a power supply line, and an EL element, the source signal line inputting its signal voltage to a gate electrode of the EL driving TFT, the power supply line supplying a current to the EL element through the source-drain of the EL driving TFT, the device characterized in that:

[0038] a signal input line, a switch, a resistor, a correction TFT, and an operation amplifier are provided;

[0039] the correction TFT has the same polarity as the EL driving TFT;

[0040] the resistor has a first terminal and a second terminal:

[0041] the operation amplifier has a non-inversion input terminal, an inversion input terminal, and an output terminal; [0042] the signal input line is connected to the first terminal of the resistor through the switch;

[0043] the second terminal of the resistor is connected to the inversion input terminal of the operation amplifier and to a source region or a drain region of the correction TFT;

[0044] of the source region and the drain region of the correction TFT, the one that is not connected to the inversion input terminal of the operation amplifier is connected to the output terminal of the operation amplifier and to the source signal line; and

[0045] a gate electrode of the correction TFT is connected to the drain region or the source region of the correction TFT. [0046] The display device may be characterized in that the electric potential of the non-inversion input terminal of the operation amplifier is equal to the electric potential of the power supply line.

[0047] The display device may be characterized in that a switching TFT is provided and that the source signal line is connected to a gate electrode of the EL driving TFT through the source-drain of the switching TFT.

[0048] The display device may be characterized in that a reset TFT is provided and that the reset TFT has a source region and a drain region one of which is connected to the output terminal of the operation amplifier and the other of which receives a given electric potential.

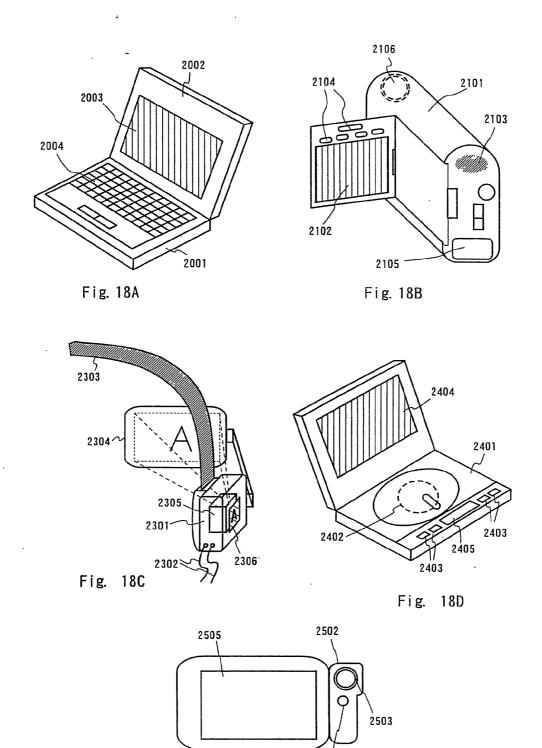

**[0049]** The present invention provides electronic equipment selected from a personal computer, a video camera, a head mounted display, an image reproducing device, and a portable information terminal, and characterized by comprising the display device described above.

#### BRIEF DESCRIPTION OF THE DRAWINGS

[0050] In the accompanying drawings:

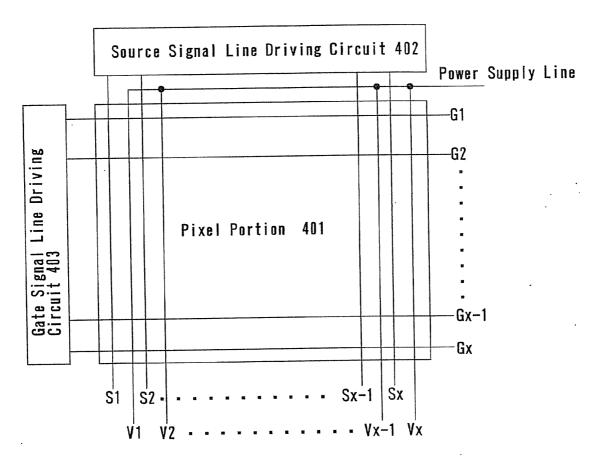

[0051] FIG. 1 is a circuit diagram showing the structure of an EL display device according to the present invention;

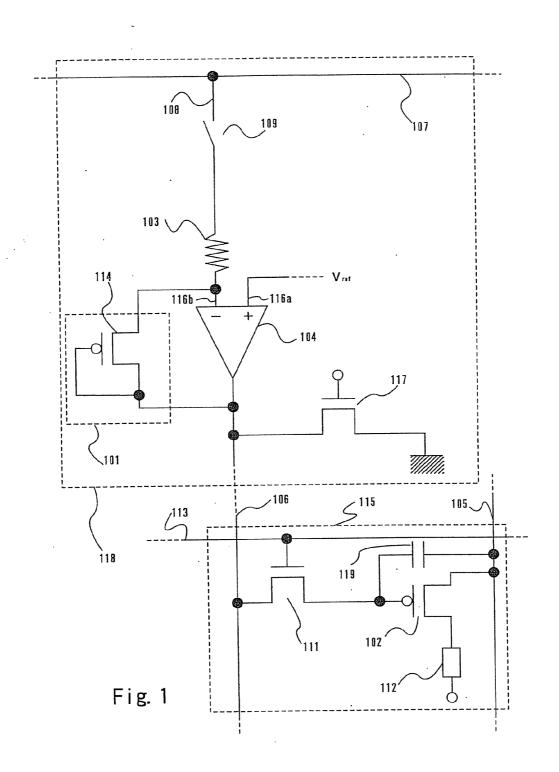

[0052] FIG. 2 is a graph showing the relation between an input voltage and the luminance of an EL element in the EL display device of the present invention;

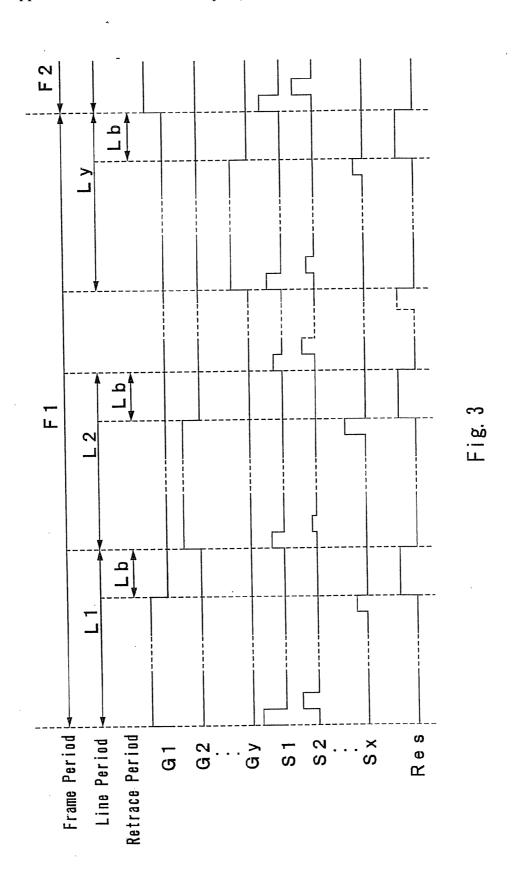

[0053] FIG. 3 is a timing chart of the EL display device according to the present invention;

[0054] FIG. 4 is a diagram showing the structure of a conventional EL display device;

[0055] FIG. 5 is a diagram showing the structure of a pixel of the conventional EL display device;

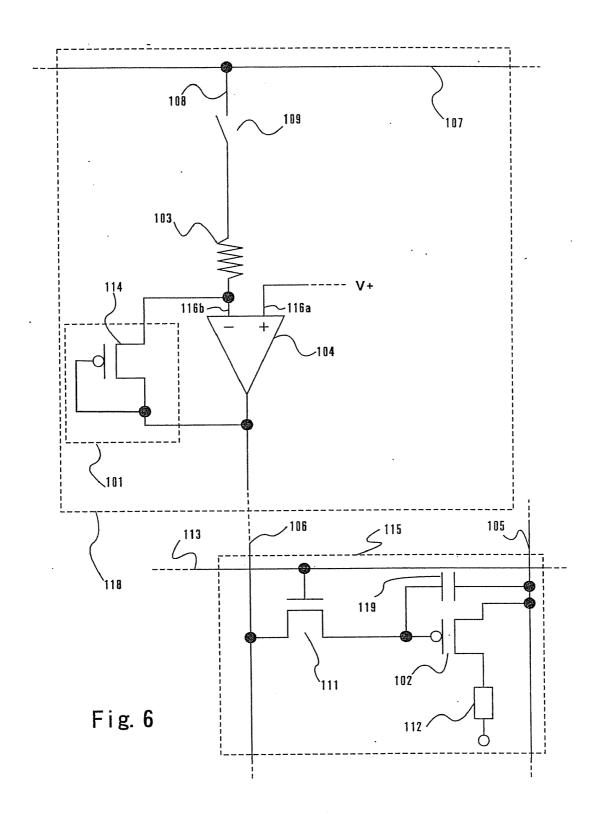

[0056] FIG. 6 is a circuit diagram showing the structure of another EL display device according to the present invention; [0057] FIG. 7 is a timing chart of the EL display device

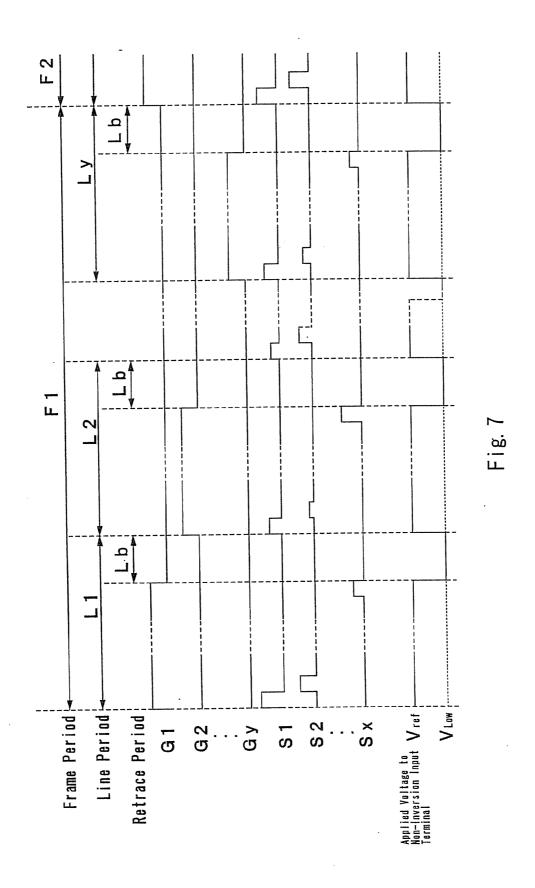

according to the present invention; [0058] FIG. 8 is a diagram showing the operation range of an EL driving TFT of analog gray scale system;

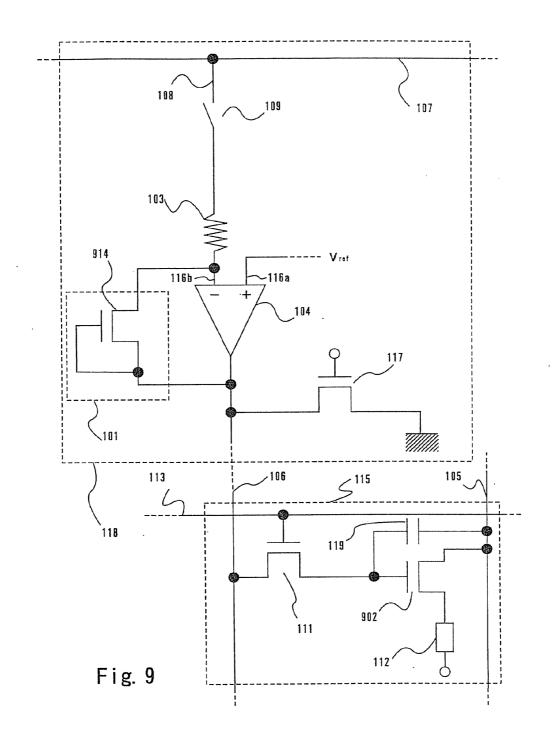

[0059] FIG. 9 is a circuit diagram showing the structure of still another EL display device according to the present invention;

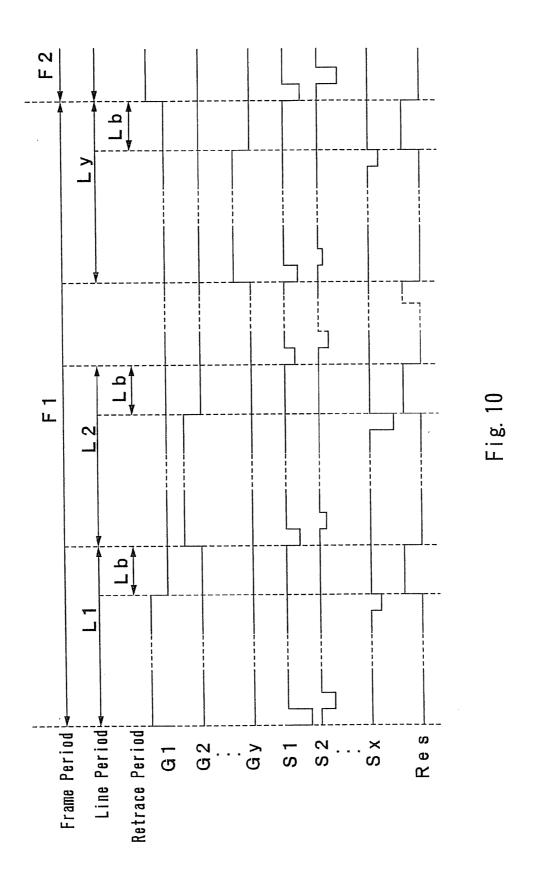

[0060] FIG. 10 is a timing chart of the EL display device according to the present invention;

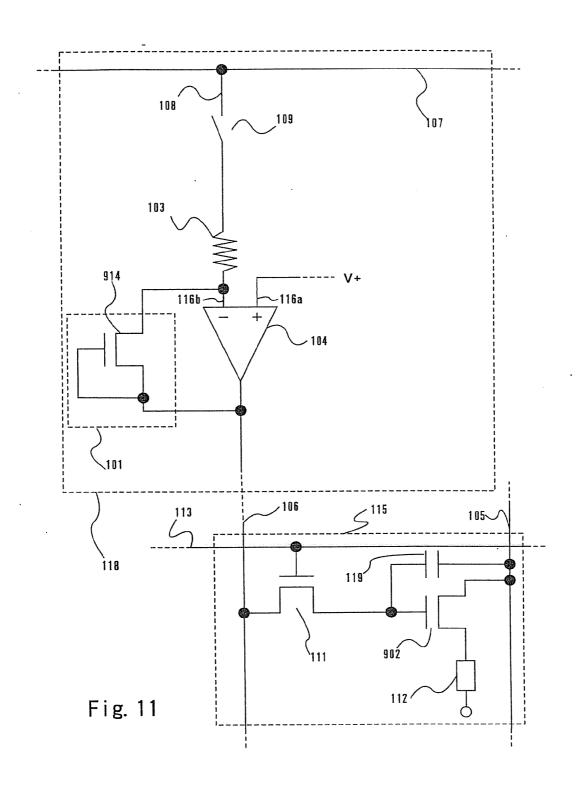

[0061] FIG. 11 is a diagram showing the structure of yet still another EL display device according to the present invention:

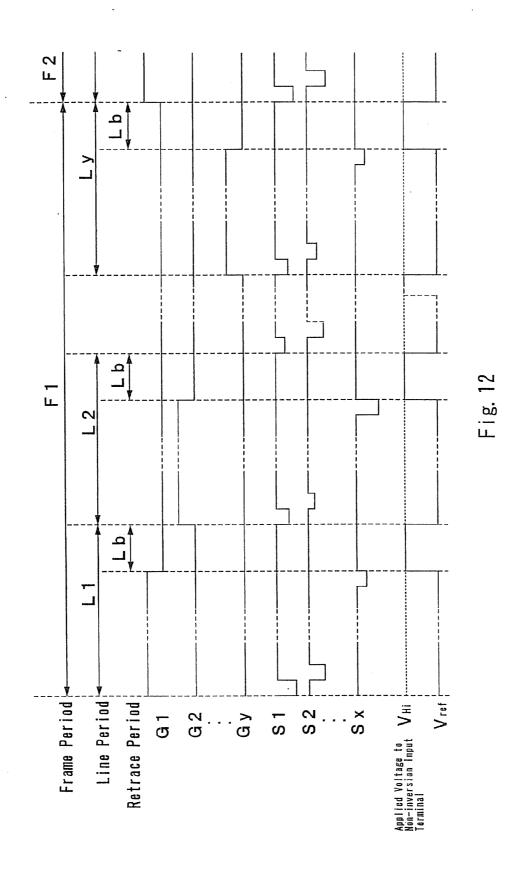

[0062] FIG. 12 is a timing chart of the EL display device according to the present invention;

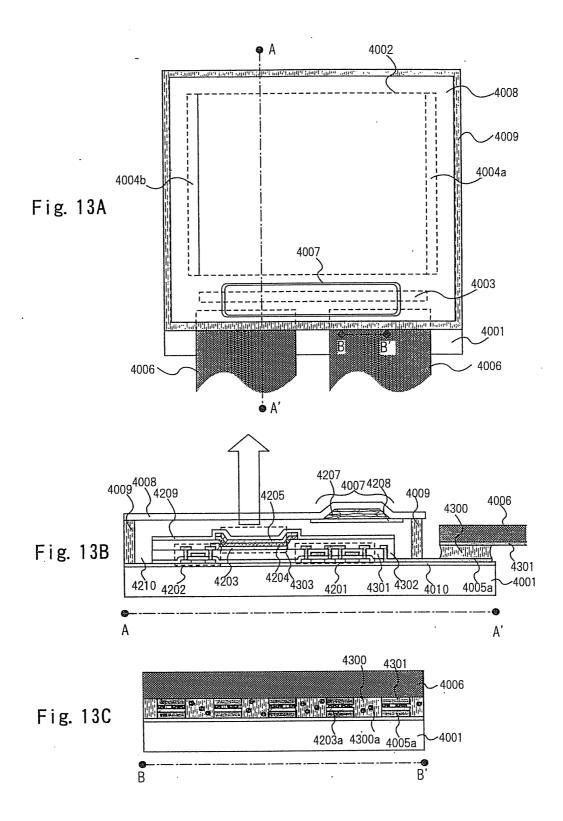

[0063] FIG. 13A is a top view of the EL display device according to the present invention and FIGS. 13B and 13C are sectional views thereof;

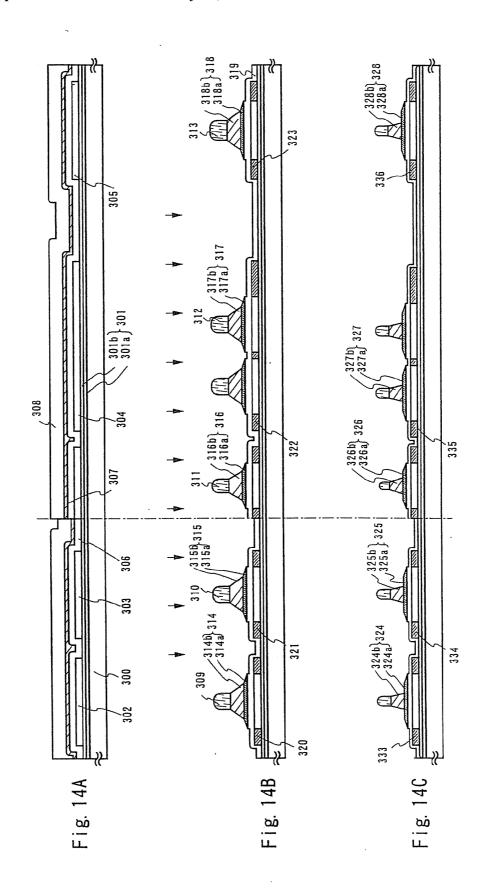

[0064] FIGS. 14A to 14C are diagrams showing a process of manufacturing an EL display device according to the present invention;

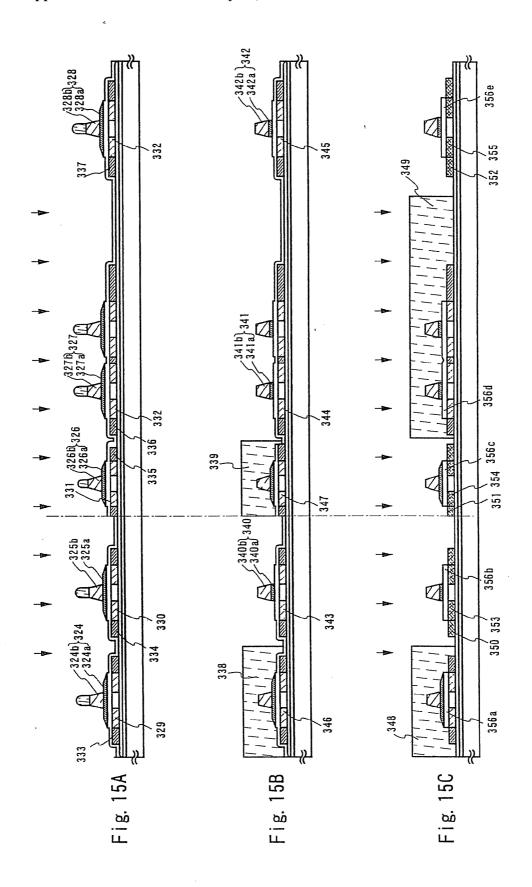

[0065] FIGS. 15A to 15C are diagrams showing the process of manufacturing an EL display device according to the present invention;

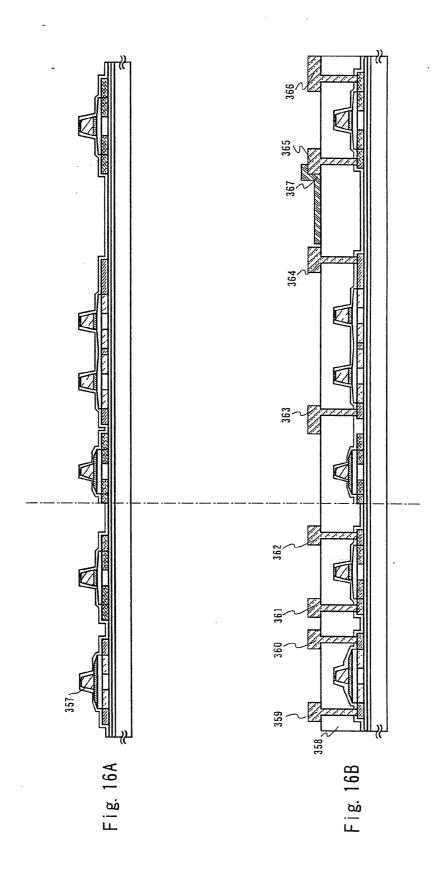

[0066] FIGS. 16A and 16B are diagrams showing the process of manufacturing an EL display device according to the present invention;

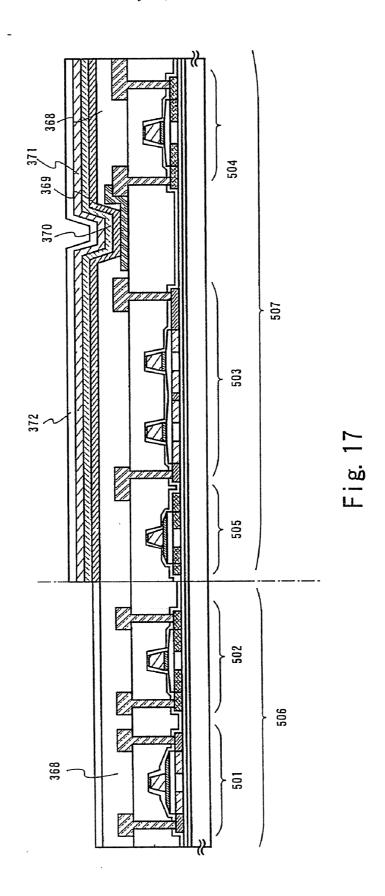

[0067] FIG. 17 is a diagram showing the process of manufacturing an EL display device according to the present invention:

[0068] FIGS. 18A to 18E are diagrams showing electronic equipment employing an EL display device of the present invention; and

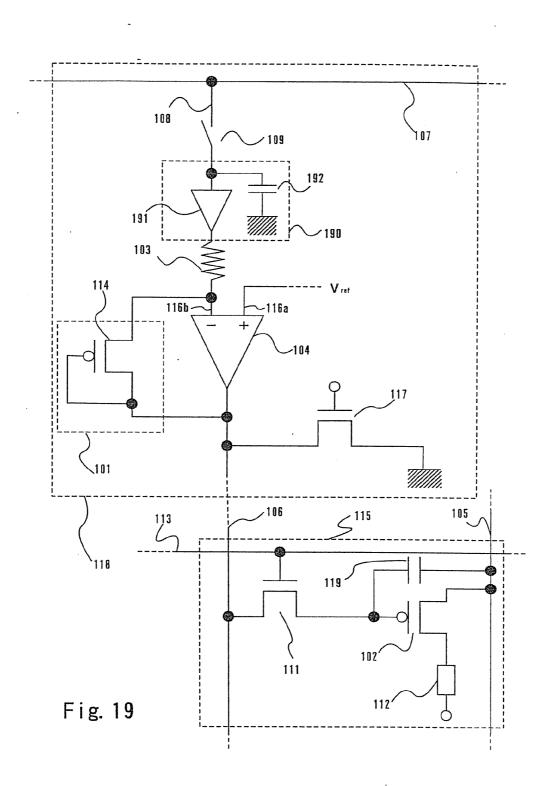

[0069] FIG. 19 is a circuit diagram showing the structure of an EL display device according to the present invention.

### DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

#### Embodiment Mode

[0070] The structure of the present invention will be described with reference to FIG. 1.

[0071] FIG. 1 shows a pixel 115 of an EL display device according to the present invention, as well as a portion 118 of a source signal line driving circuit for inputting a signal to the pixel.

[0072] The portion 118 of the source signal line driving circuit is composed of a diode 101, a resistor 103, an operation amplifier 104, an analog signal input line (signal input line) 107, a signal line 108, a switch (switching element) 109, and a reset TFT 117. The diode 101 consists of a correction TFT 114 in which a gate electrode and a drain region are electrically connected to each other.

[0073]  $\,$  The correction TFT 114 is a p-channel TFT. The reset TFT 117 may either be a p-channel TFT or an n-channel TFT

[0074] The pixel is composed of an EL driving TFT 102, a power supply line (power line) 105, a source signal line 106, a gate signal line 113, a switching TFT 111, an EL element 112, and a capacitor 119. The EL driving TFT 102 is a p-channel TFT. The switching TFT 111 may either be a p-channel TFT or an n-channel TFT.

[0075] The EL driving TFT and the correction TFT are both p-channel TFTs here, but n-channel TFTs may be used for the EL driving TFT and the correction TFT. However, the EL driving TFT and the correction TFT have to have the same polarity and almost the same threshold voltage.

[0076] The analog signal input line 107 is connected to the signal line 108, which is connected through the switch 109 to the resistor 103. The resistor 103 is connected to an inversion input terminal 116b of the operation amplifier 104. The inversion input terminal 116b of the operation amplifier 104 is connected to a source region of the correction TFT 114. The operation amplifier 104 has a non-inversion input terminal 116a, to which a reference electric potential  $V_{ref}$  is inputted. An output terminal of the operation amplifier 104 is connected to a drain region of the correction TFT 114 and to the source signal line 106. The reset TFT 117 has a source region

and a drain region one of which is connected to the source signal line 106 and the other of which is grounded.

[0077] The switching TFT 111 has a gate electrode connected to the gate signal line 113. The switching TFT 111 also has a source region and a drain region one of which is connected to the source signal line 106 and the other of which is connected to a gate electrode of the EL driving TFT 102 and to one of two electrodes of the capacitor 119. The EL driving TFT 102 has a source region connected to the power supply line 105 and has a drain region connected to an anode of the EL element 112. The other electrode of the capacitor 119 is connected to the power supply line 105. A cathode of the EL element 112 is connected to a reference power line, which is not shown in FIG. 1.

[0078] A method of driving the display device shown in FIG. 1 will be described.

[0079] A signal voltage  $V_{in}$ , of a video signal inputted to the analog signal input line 107 is sampled when the switch 109 is opened or closed. The signal voltage is then inputted to the signal line 108.

[0080] The signal electric potential  $V_{in}$  here is equal to or larger than the reference electric potential  $V_{ref}$  A signal having a greater  $V_{in}$  value represents a higher luminance.

[0081] The inversion input terminal 116b and the output terminal of the operation amplifier 104 are connected to each other through the diode 101. Therefore the electric potential of the inversion input terminal 116b is the same as the electric potential of the non-inversion input terminal 116a. In other words, the electric potential of the inversion input terminal 116b is equal to the reference electric potential  $V_{ref}$ . Then the voltage in the resistor 103 is  $V_{in}$ - $V_{ref}$  and a current  $I_f$  expressed as Equation 2 flows through the resistor 103.

$$I_1 = (V_{in} - V_{ref})/R \tag{Equation 2}$$

[0082] The current  $I_1$  flows through the resistor from the side connected to the analog signal input line 107 toward the side connected to the inversion input terminal 116b.

[0083] R represents the resistance of the resistor 103. The current  $I_1$  is inputted to the diode 101. The drain current of the correction TFT 114 that constitutes the diode 101 corresponds to the current  $I_1$ . Since the drain region and the gate electrode are connected to each other in the correction TFT 114, the gate voltage of the TFT 114 is equal to the drain-source voltage thereof. Therefore the correction TFT 114 operates in the saturation range.

[0084] Being a p-channel TFT, the correction TFT 114 is not turned conductive unless the electric potential of the correction TFT becomes higher on the side connected to the inversion input terminal 116b of the operation amplifier 104 than the side connected to the output terminal of the operation amplifier 104.

[0085] Therefore the correction TFT on the side connected to the inversion input terminal 116b of the operation amplifier 104 serves as a source region whereas the side connected to the output terminal of the operation amplifier 104 serves as a drain region. The correction TFT thus functions as a diode that allows a current to flow in only one direction.

**[0086]** Equation 1 given in the above is applicable to a TFT that operates in the saturation range. The gate voltage is obtained by transforming Equation 1. Based on this transformation, the gate voltage  $V_{GS1}$  when the drain current is  $I_1$  is obtained by Equation 3.

$$V_{GS1} = -\sqrt{2I_1(1/\mu_0C_0(L_1/W_1) + V_{th})}$$

(Equation 3)

wherein,  $W_1$  represents the gate width of the correction TFT 114,  $L_1$  represents the gate length of the correction TFT 114, and  $V_{\it th1}$  represents the threshold voltage of the correction TFT 114.

**[0087]** However, the gate voltage  $V_{GS1}$  and the threshold voltage  $V_{th1}$  are usually 0 or smaller since the correction TFT **114** here is a p-channel TFT.

[0088] Initially, the reset TFT 117 is conductive and the electric potential of the source signal line 106 is set to 0 V.

[0089] Then the reset TFT 117 is turned unconductive. Since the gate voltage and the drain-source voltage are equal to each other in the correction TFT 114, an electric potential  $V_{ref}V_{GS1}$  (the reference electric potential shifted by the voltage  $V_{GS1}$ ) is inputted to the source signal line.

[0090] Before the electric potential  $V_{ref}V_{GS1}$  is inputted to the source signal line 106, the electric potential of the source signal line 106 is set to 0 V by turning the reset TFT 117 conductive. This is carried out in anticipation for the case in which the electric potential of the source signal line 106 in a certain state is raised higher than the electric potential of the inversion input terminal 116b of the operation amplifier 104 determined by a signal electric potential next inputted to the analog signal input line 107. In this case, the source region and the drain region interchanges their places in the correction TFT 114 to make the correction TFT 114 unconductive and block feedback between the input and output of the operation amplifier 104. The invention avoids this situation by setting the electric potential of the source signal line to 0 V initially.

[0091] The electric potential given to the output terminal of the operation amplifier 104 when the reset TFT 117 is turned conductive is not limited to 0 V. In general, the output terminal receives an electric potential set equal to or lower than the lowest electric potential outputted to the source signal line (hereinafter referred to as lowest electric potential  $V_{SLOW}$ ) which corresponds to the highest electric potential of the signal inputted to the analog signal input line. In other words, the electric potential of the output terminal of the operation amplifier 104 is set so as to be equal to or lower than the lowest electric potential  $V_{SLOW}$  by turning the reset TFT 117 conductive

[0092] The operation of setting the electric potential of the output terminal of the operation amplifier to the lowest electric potential  $V_{SLOW}$  so that the correction TFT that is a p-channel TFT is always conductive is called a reset operation in this specification.

[0093] The reset operation can be carried out during the retrace period (horizontal retrace period) or other times.

[0094] The electric potential  $V_{ref}$   $V_{GSI}$  inputted to the source signal line 106 is inputted to the capacitor 119 and to the gate electrode of the EL driving TFT 102 through the switching TFT 111, which has been turned conductive upon input of a signal to the gate signal line 113. The electric potential of the power supply line 105 (power supply electric potential) is set to the same level as the reference electric potential  $V_{ref}$  Accordingly, the source region of the EL driving TFT 102 in a conductive state has an electric potential equal to  $V_{ref}$

[0095] At this point, a gate voltage  $V_{GS2}$  of the EL driving TFT 102 is equal to the gate voltage  $V_{GS1}$  of the correction TFT 114

[0096] If the EL driving TFT 102 also operates in the saturation range, Equation 1 is applicable to the TFT 102. The drain current of the TFT 102 in this case is given as  $I_2$ , which is obtained by Equation 4.

$$I_2 = (1/2)\mu_0 C_0 (W_2/L_2)(V_{Gs1} - V_{th2})^2$$

(Equation 4)

wherein,  $V_{th2}$  represents the threshold voltage of the EL driving TFT 102, and  $W_2$  and  $L_2$  represent the gate width and the gate length of the EL driving TFT 102, respectively.

**[0097]** If the threshold voltage  $V_{th1}$  of the correction TFT **114** is almost equal to the threshold voltage  $V_{th2}$  of the EL driving TFT **102**, the drain current  $I_2$  of the EL driving TFT **102** is independent of the threshold voltage of the two TFTs as shown in Equation 5.

$$I_2 = I_1(W_2/L_2)(L_1/W_1)$$

(Equation 5)

[0098] In this way, the current  $I_2$  that corresponds to the current  $I_1$  linearly can be inputted to the EL element 112.

[0099] Equation 2 shows that the current  $I_1$  is in proportion to the input electric potential  $V_m$ . FIG. 2 is a graph showing the relation between the signal electric potential  $V_m$  of a video signal and the luminance of the EL element in the EL display device structured as above. The axis of abscissa indicates the signal electric potential  $V_m$  of the video signal and the axis of ordinate indicates the luminance of the EL element. As the graph shows, the EL element 112 can emit light at a luminance linearly corresponding to the input voltage  $V_m$ .

[0100] FIG. 3 is a timing chart illustrating the operation of the EL display device structured as shown in FIG. 1. The EL display device has source signal lines S1 to Sx (x lines in total), power supply lines V1 to Vx (x lines in total), and gate signal lines G1 to Gy (y lines in total).

[0101] The switching TFT and the reset TFT here are n-channel TFTs. If p-channel TFTs are used for the switching TFT and the reset TFT; the phase of the signals inputted to the gate signal lines G1 to Gy and to the gate electrode of the reset TFT is reversed.

[0102] First, signals are inputted to the gate signal line G1 to turn every switching TFT that is connected to the gate signal line G1 conductive. The period during which the gate signal line G1 is selected is called a first line period L1. In the first line period L1, signals inputted from the analog signal input line are sequentially inputted to the source signal lines S1 to Sx. Each EL element emits light at a luminance corresponding to the inputted signal electric potential.

[0103] After inputting the signals to all of the source signal lines S1 to Sx is completed, a retrace period Lb is provided in order to input signals to the source signal lines again starting from S1. During the retrace period Lb, a signal Res is inputted to the gate electrode of the reset TFT to turn the reset TFT conductive, so that the electric potential is set to 0 V in all of the source signal lines S1 to Sx.

[0104] Thereafter, signals are inputted to the gate signal line G2 to turn every switching TFT that is connected to the gate signal line G2 conductive. Thus started is a second line period L2. Similar to the first line period L1, signals inputted from the analog signal input line are sequentially inputted to the source signal lines S1 to Sx during the second line period L2. Each EL element emits light at a luminance corresponding to the inputted signal electric potential.

[0105] After inputting the signals to all of the source signal lines S1 to Sx is completed, a retrace period Lb is provided in order to input signals to the source signal lines again starting from S1. During the retrace period Lb, a signal Res is inputted to the gate electrode of the reset TFT to turn the reset TFT

conductive, so that the electric potential is set to  $0\,\mathrm{V}$  in all of the source signal lines S1 to Sx.

[0106] The same operation is repeated for all of the gate signal lines G1 to Gy to display one image. A period the display device takes to display one image is called one frame period. The operations above completes one frame period F1.

[0107] After completion of the frame period F1, the gate signal line G1 is again selected to start a second frame period F2.

[0108] The EL display device shown in FIG. 1 in accordance with the present invention displays images by repeating the above operations.

[0109] A buffer circuit 190 may be placed between the switch 109 and the resistor 103 as shown in FIG. 19. The buffer circuit 190 is composed of a buffer 191 and a capacitor 192

[0110] Embodiments of the present invention will be described below.

#### Embodiment 1

[0111] This embodiment describes with reference to FIG. 9 a case of using n-channel TFTs for the correction TFT and the EL driving TFT in FIG. 1. Components in FIG. 9 that are identical with those in FIG. 1 are denoted by the same symbols.

[0112] FIG. 9 shows a pixel 115 of an EL display device according to the present invention, as well as a portion 118 of a source signal line driving circuit for inputting a signal to the pixel.

[0113] The portion 118 of the source signal line driving circuit is composed of a diode 101, a resistor 103, an operation amplifier 104, an analog signal input line 107, a signal line 108, a switch 109, and a reset TFT 117. The diode 101 consists of a correction TFT 914 in which a gate electrode and a drain region are electrically connected to each other.

[0114] The correction TFT 914 is an n-channel TFT. The reset TFT 117 may either be a p-channel TFT or an n-channel TFT.

[0115] The pixel 115 is composed of an EL driving TFT 902, a power supply line 105, a source signal line 106, a switching TFT 111, an EL element 112, a gate signal line 113, and a capacitor 119. The EL driving TFT 902 is an n-channel TFT. The switching TFT 111 may either be a p-channel TFT or an n-channel TFT.

[0116] The analog signal input line 107 is connected to the signal line 108, which is connected through the switch 109 to the resistor 103. The resistor 103 is connected to an inversion input terminal 116b of the operation amplifier 104. The inversion input terminal 116b of the operation amplifier 104 is connected to a source region of the correction TFT 914. The operation amplifier 104 has a non-inversion input terminal 116a, to which a reference electric potential  $V_{ref}$  is inputted. An output terminal of the operation amplifier 104 is connected to a drain region of the correction TFT 914 and to the source signal line 106. The reset TFT 117 has a source region and a drain region one of which is connected to the source signal line 106 and the other of which is grounded.

[0117] The switching TFT 111 has a gate electrode connected to the gate signal line 113. The switching TFT 111 also has a source region and a drain region one of which is connected to the source signal line 106 and the other of which is connected to a gate electrode of the EL driving TFT 902 and to one of two electrodes of the capacitor 119. The EL driving TFT 902 has a source region connected to the power supply

line 105 and has a drain region connected to a cathode of the EL element 112. The other electrode of the capacitor 119 is connected to the power supply line 105. An anode of the EL element 112 is connected to a reference power line, which is not shown in FIG. 9.

[0118] A method of driving the display device shown in FIG. 9 will be described.

[0119] A signal voltage  $V_{in}$  of a video signal inputted to the analog signal input line 107 is sampled when the switch 109 is opened or closed. The signal voltage is then inputted to the signal line 108.

**[0120]** In this embodiment, the signal electric potential  $V_{\mathit{in}}$  is equal to or smaller than the reference electric potential  $V_{\mathit{ref}}$ . A signal having a smaller  $V_{\mathit{in}}$  value represents a higher luminance.

[0121] The inversion input terminal 116b and the output terminal of the operation amplifier 104 are connected to each other through the diode 101. Therefore the electric potential of the inversion input terminal 116b is the same as the electric potential of the non-inversion input terminal 116a. In other words, the electric potential of the non-inversion input terminal 116b is equal to the reference electric potential  $V_{ref}$ . Then, the voltage in the resistor 103 is  $V_{ref}$ - $V_{in}$  and a current  $I_1$  expressed as Equation 6 flows through the resistor 103.

$$I_1 = (V_{ref} - V_{in})/R \tag{Equation 6}$$

[0122] In this embodiment, the current  $I_1$  flows through the resistor from the side connected to the inversion input terminal 116b of the operation amplifier 104 toward the side connected to the analog signal input line 107.

[0123] Herein, R represents the resistance of the resistor 103. The current  $I_1$  flows through the diode 101. The drain current of the correction TFT 914 that constitutes the diode 101 corresponds to the current L. Since the drain region and the gate electrode are connected to each other in the correction TFT 914, the gate voltage of the TFT 914 is equal to the drain-source voltage thereof. Therefore the correction TFT 914 operates in the saturation range.

[0124] Being an n-channel the correction TFT 914 is not turned conductive unless the electric potential of the correction TFT becomes lower on the side connected to the inversion input terminal 116b of the operation amplifier 104 than the side connected to the output terminal of the operation amplifier 104.

[0125] Therefore the correction TFT 914 on the side connected to the inversion input terminal 116b of the operation amplifier 104 serves as a source region whereas the side connected to the output terminal of the operation amplifier 104 serves as a drain region. The correction TFT thus functions as a diode that allows a current to flow in only one direction.

**[0126]** Equation 1 given in the above is applicable to a TFT that operates in the saturation range. The gate voltage is obtained by transforming Equation 1. Based on this transformation, the gate voltage  $V_{GS1}$  when the drain current is  $I_1$  is obtained by Equation 7.

$$V_{GS1} = \sqrt{2I_1(1/\mu_0C_0)(L_1/W_1)} + V_{th1}$$

(Equation 7)

where,  $W_1$  represents the gate width of the correction TFT 914,  $L_1$  represents the gate length of the correction TFT 914, and  $V_{m1}$  represents the threshold voltage of the correction TFT 914.

[0127] Initially, the reset TFT 117 is conductive and the electric potential of the source signal line 106 is set to 0 V.

[0128] Then the reset TFT 117 is turned unconductive. Since the gate voltage and the drain-source voltage are equal to each other in the correction TFT 914, an electric potential  $V_{ref}V_{GS1}$  (the reference electric potential  $V_{ref}$  shifted by the voltage  $V_{GS1}$ ) is inputted to the source signal line 106.

[0129] Before the electric potential  $V_{ref}+V_{GS1}$  is inputted to the source signal line 106, the electric potential of the source signal line 106 is set to 0 V by the reset TFT 117. This is carried out in anticipation for the case in which the electric potential of the source signal line 106 in a certain state is reduced lower than the electric potential of the inversion input terminal 116b of the operation amplifier 104 changed by a signal electric potential inputted next. In this case, the source region and the drain region interchange their places in the correction TFT 914 to make the correction TFT 914 unconductive and block feedback between the input and output of the operation amplifier 104. The present invention avoids this situation by setting the electric potential of the source signal line to 0 V during the retrace period (horizontal retrace period)

[0130] The electric potential given to the output terminal of the operation amplifier 104 when the reset TFT 117 is turned conductive is not limited to 0 V. In general, the output terminal receives an electric potential set equal to or higher than the highest electric potential outputted to the source signal line (hereinafter referred to as highest electric potential  $V_{SHI}$ ) which corresponds to the lowest electric potential of the signal inputted to the analog signal input line. In other words, the electric potential of the output terminal of the operation amplifier 104 is set so as to be equal to or higher than the highest electric potential  $V_{SHI}$  by turning the reset TFT 117 conductive.

[0131] The operation of setting the electric potential of the output terminal of the operation amplifier to the highest electric potential so that the correction TFT that is an n-channel TFT is always conductive is called a reset operation.

[0132] The electric potential  $V_{ref}+V_{GS1}$  inputted to the source signal line 106 is inputted to the Capacitor 119 and to the gate electrode of the EL driving TFT 902 through the switching TFT 111, which has been turned conductive upon input of a signal to the gate signal line 113. The electric potential of the power supply line 105 (power supply electric potential) is set to the same level as the reference electric potential  $V_{ref}$ . Accordingly, the source region of the EL driving TFT 902 in a conductive state has an electric potential equal to  $V_{ref}$ .

[0133] At this point, a gate voltage  $V_{GS2}$  of the EL driving TFT 902 is equal to the gate voltage  $V_{GS1}$  of the correction TFT 914. If the EL driving TFT 902 also operates in the saturation range, Equation 1 is applicable to the TFT 902. The drain current of the TFT 902 in this case is given as  $I_2$ , which is obtained by Equation 8.

$$I_2 = (1/2)\mu_0 C_0(W_2/L_2)(V_{GS1} - V_{th2})^2$$

(Equation 8)

where,  $V_{\it th2}$  represents the threshold voltage of the EL driving TFT 902, and  $W_2$  and  $L_2$  represent the gate width and the gate length of the EL driving TFT 902, respectively.

[0134] If the threshold voltage  $V_{\it th1}$  of the correction TFT 914 is almost equal to the threshold voltage  $V_{\it th2}$  of the EL driving TFT 902, the drain current  $I_2$  of the EL driving TFT 902 is independent of each threshold voltage of the two TFTs as shown in Equation 9.

$$I_2 = I_1(W_2/L_2)(L_1/W_1)$$

(Equation 9)

[0135] In this way, the current  $I_2$  that corresponds to the current  $I_1$  linearly can be inputted to the EL element 112.

[0136] Equation 6 shows that the current  $I_1$  is in proportion to the input electric potential  $V_{in}$ . Thus the EL element 112 can emit light at a luminance linearly corresponding to the input potential  $V_{in}$ .

[0137] FIG. 10 is a timing chart illustrating the operation of the EL display device structured as shown in FIG. 9. The EL display device has source signal lines S1 to Sx (x lines in total), power supply lines V1 to Vx (x lines in total), and gate signal lines G1 to Gy (y lines in total).

[0138] The switching TFT 111 and the reset TFT 117 here are n-channel TFTs. If p-channel TFTs are used for the switching TFT and the reset TFT, the phase of the signals inputted to the gate signal lines G1 to Gy and to the gate electrode of the reset TFT 117 is reversed.

[0141] Thereafter, signals are inputted to the gate signal line G2 to turn every switching TFT 111 that is connected to the gate signal line G2 conductive. Thus started is a second line period L2. Similar to the first line period L1, signals inputted from the analog signal input line 107 are sequentially inputted to the source signal lines S1 to Sx during the second line period L2. Each EL element 112 emits light at a luminance corresponding to the inputted signal electric potential. [0142] After inputting the signals to all of the source signal lines S1 to Sx is completed, a retrace period Lb is provided in order to input signals to the source signal lines again starting from S1. During the retrace period Lb, a signal Res is inputted to the gate electrode of the reset TFT to turn the reset TFT conductive, so that the electric potential is set to 0 V in all of the source signal lines S1 to Sx.

[0143] The same operation is repeated for all of the gate signal lines G1 to Gy to display one image. A period the display device takes to display one image is called one frame period. The operation above completes one frame period F1.

[0144] After completion of the frame period F1, the gate signal line G1 is again selected to start a second frame period F2.

[0145] The EL display device shown in FIG. 9 in accordance with the present invention displays images by repeating the above operations.

#### Embodiment 2

[0146] This embodiment describes a driving circuit having a structure different from the one in FIG. 1.

[0147] FIG. 6 shows the structure of the driving circuit according to this embodiment. Components in FIG. 6 that are identical with those in FIG. 1 are denoted by the same sym-

bols and explanations thereof are omitted. Unlike FIG. 1, the reset TFT 117 is not provided in FIG. 6.

[0148] For that reason, measures other than the reset TFT are taken to reduce the electric potential of the source signal line 106 prior to input of a signal to a level lower than the electric potential of the inversion input terminal 116b of the operation amplifier 104 determined by a video signal inputted next. The period assigned to reduce the electric potential of the source signal line 106 prior to input of a signal to a level lower than the electric potential of the inversion input terminal 116b of the operation amplifier 104 determined by a video signal inputted next, is called a reset period.

[0149] In FIG. 6, an electric potential  $V_+$  inputted to the non-inversion input terminal 106a of the operation amplifier 104 is kept at the reference electric potential  $V_{ref}$  while a video signal is sampled. On the other hand,  $V_+$  is reduced to an electric potential  $V_{LOW}$  during the reset period. The electric potential  $V_{LOW}$  is always set to a level lower than the electric potential of the inversion input terminal 116b of the operation amplifier 104 whatever electric potential the inversion input terminal takes due to a video signal inputted from the external

[0150] Therefore the electric potential  $V_{LOW}$  is set to a level equal to or lower than the reference electric potential  $V_{ref}$

[0151] In the reset period, the electric potential of the non-inversion input terminal 106a of the operation amplifier 104 is equal to the electric potential  $V_{LOW}$ .

[0152] Then the electric potential of the non-inversion input terminal 116a is lower than the electric potential of the inversion input terminal 1016b to cause the operation amplifier 104 to output a low power supply electric potential. In this way, the output terminal of the operation amplifier is kept to a sufficiently low electric potential.

[0153] The electric potential of the source signal line 106 is thus reduced to a level equal to or lower than  ${\rm V}_{LOW}$ .

[0154] After the reset period, the electric potential of the non-inversion input terminal 116a of the operation amplifier 104 is returned to  $V_{ref}$  and then a video signal is inputted. Since the electric potential of the inversion input terminal 116b of the operation amplifier 104 is always higher than the electric potential  $V_{LOW}$ , the diode 101 keeps operating in a conductive state (without being accidentally turned unconductive) to effect feedback between the input and output of the operation amplifier 104. The operation amplifier thus operates so as to equalize the electric potential of the non-inversion input terminal 116a with the electric potential of the inversion input terminal 116b.

[0155] The reset period is provided within the retrace period (horizontal retrace period).

[0156] The other operations are the same as those in Embodiment Mode.

[0157] FIG. 7 is a timing chart illustrating the operation of the EL display device structured as shown in FIG. 6. The EL display device has source signal lines S1 to Sx (x lines in total), power supply lines V1 to Vx (x lines in total), and gate signal lines G1 to Gy (y lines in total).

[0158] The switching TFT 111 here is an n-channel TFT. If a p-channel TFT is used for the switching TFT, the phase of the signal inputted to the gate signal lines G1 to Gy is reversed.

[0159] First, signals are inputted to the gate signal line G1 to turn every switching TFT 111 that is connected to the gate signal line G1 conductive. The period during which the gate signal line G1 is selected is called a first line period L1. In the

first line period L1, signals inputted from the analog signal input line 107 are sequentially inputted to the source signal lines S1 to Sx. Each EL element 112 emits light at a luminance corresponding to the inputted signal electric potential. [0160] After inputting the signals to all of the source signal lines S1 to Sx is completed, a retrace period (horizontal retrace period) Lb is provided in order to input signals to the source signal lines again starting from S1. During the retrace period Lb, the electric potential  $V_{LOW}$  is inputted to the non-inversion input terminal 116a of the operation amplifier 104 to set the electric potential to a level equal to or lower than  $V_{LOW}$  in all of the source signal lines S1 to Sx.

[0161] Thereafter, signals are inputted to the gate signal line G2 to turn every switching TFT 111 that is connected to the gate signal line G2 conductive. Thus started is a second line period L2. Similar to the first line period L1, signals inputted from the analog signal input line 107 are sequentially inputted to the source signal lines S1 to Sx during the second line period L2. Each EL element 112 emits light at a luminance corresponding to the inputted signal electric potential. [0162] After inputting the signals to all of the source signal lines S1 to Sx is completed, a retrace period Lb is provided in order to input signals to the source signal lines again starting from S1. During the retrace period Lb, the electric potential  $V_{LOW}$  is inputted to the non-inversion input terminal 116a of the operation amplifier 104 to set the electric potential to a level equal to or lower than  $V_{LOW}$  in all of the source signal lines S1 to Sx.

[0163] The same operation is repeated for all of the gate signal lines G1 to Gy to display one image. A period the display device takes to display one image is called one frame period. The operations above complete a first frame period F1

[0164] After completion of the first frame period F1, the gate signal line G1 is again selected to start a second frame period F2.

[0165] The EL display device shown in FIG. 6 in accordance with the present invention displays images by repeating the above operations.

#### **Embodiment 3**

[0166] This embodiment describes a driving circuit having a structure different from the one in FIG. 9.

[0167] FIG. 11 shows the structure of the driving circuit according to this embodiment. Components in FIG. 11 that are identical with those in FIG. 9 are denoted by the same symbols and explanations thereof are omitted. Unlike in FIG. 9, no reset TFT 117 is provided in FIG. 11.

[0168] For that reason, measures other than the reset TFT are taken to raise the electric potential of the source signal line 106 prior to input of a signal to a level higher than the electric potential of the inversion input terminal 116b of the operation amplifier 104 determined by a video signal inputted next. The period assigned to raise the electric potential of the source signal line 106 prior to input of a signal to a level higher than the electric potential of the inversion input terminal 116b of the operation amplifier 104 determined by a video signal inputted next, is called a reset period.

[0169] In FIG. 11, an electric potential inputted to the non-inversion input terminal 106a of the operation amplifier 104 is kept at the reference electric potential  $V_{ref}$  while a video signal is sampled. On the other hand, is raised to an electric potential  $V_{Hi}$  during the reset period. The electric potential  $V_{Hi}$  is always set to a level higher than the electric potential of

the inversion input terminal 116b of the operation amplifier 104 whatever electric potential the inversion input terminal takes due to a video signal inputted from the external.

[0170] In other words, the electric potential  $V_{Hi}$  is set to a level equal to or higher than the reference electric potential  $V_{ref}$

[0171] Then the electric potential of the non-inversion input terminal 106a is higher than the electric potential of the inversion input terminal 106b to cause the operation amplifier 104 to output a high power supply electric potential. In this way, the output terminal of the operation amplifier is kept to a sufficiently high electric potential.

[0172] In the reset period, the electric potential of the output terminal of the operation amplifier 104 is equal to or higher than  $V_{Hi}$ . After the reset period, the electric potential of the non-inversion terminal 116a of the operation amplifier 104 is returned to  $V_{ref}$  and then a video signal is inputted. Since the electric potential of the inversion input terminal 116b of the operation amplifier 104 is always lower than the electric potential  $V_{Hi}$ , the diode 101 keeps operating in a conductive state (without being accidentally turned unconductive) to effect feedback between the input and output of the operation amplifier 104. The operation amplifier thus operates so as to equalize the electric potential of the inversion input terminal 116a with the electric potential of the inversion input terminal 116b.

[0173] The reset period is provided within the retrace period (horizontal retrace period).

[0174] The other operations are the same as those in Embodiment 1.

[0175] FIG. 12 is a timing chart illustrating the operation of the EL display device structured as shown in FIG. 11. The EL display device has source signal lines S1 to Sx (x lines in total), power supply lines V1 to Vx (x lines in total), and gate signal lines G1 to Gy (y lines in total).

[0176] The switching TFT 111 here is an n-channel TFT. If a p-channel TFT is used for the switching TFT, the phase of the signal inputted to the gate signal lines G1 to Gy is reversed.

[0177] First, signals are inputted to the gate signal line G1 to turn every switching TFT 111 that is connected to the gate signal line G1 conductive. The period during which the gate signal line G1 is selected is called a first line period L1. In the first line period L1, signals inputted from the analog signal input line 107 are sequentially inputted to the source signal lines S1 to Sx. Each EL element EL emits light at a luminance corresponding to the inputted signal electric potential.

[0178] After inputting the signals to all of the source signal lines S1 to Sx is completed, a retrace period (horizontal retrace period) Lb is provided in order to input signals to the source signal lines again starting from S1. During the retrace period Lb, the electric potential  $V_{Hi}$  is inputted to the non-inversion input terminal 116a of the operation amplifier 104 to set the electric potential to a level equal to or higher than  $V_{Hi}$  in all of the source signal lines S1 to Sx.

[0179] Thereafter, signals are inputted to the gate signal line G2 to turn every switching TFT 111 that is connected to the gate signal line G2 conductive. Thus started is a second line period L2. Similar to the first line period L1, signals inputted from the analog signal input line 107 are sequentially inputted to the source signal lines S1 to Sx during the second line period L2. Each EL element 112 emits light at a luminance corresponding to the inputted signal electric potential.

[0180] After inputting the signals to all of the source signal lines S1 to Sx is completed, a retrace period Lb is provided in order to input signals to the source signal lines again starting from S1. During the retrace period Lb, the electric potential  $V_{Hi}$  is inputted to the non-inversion input terminal 116a of the operation amplifier 104 to set the electric potential to a level equal to or higher than  $V_{Hi}$  in all of the source signal lines S1 to Sx.

[0181] The same operation is repeated for all of the gate signal lines G1 to Gy to display one image. A period the display device takes to display one image is called one frame period. The operations above complete a first frame period F1.

[0182] After completion of the first frame period F1, the gate signal line G1 is again selected to start a second frame period F2.

[0183] The EL display device shown in FIG. 11 in accordance with the present invention displays images by repeating the above operations.

#### **Embodiment 4**

**[0184]** In this embodiment, a method of simultaneously manufacturing This (n-channel TFT and p-channel in a pixel portion and a driver circuit provided in the periphery of the pixel portion on the same substrate in the EL display of the present invention is described in detail with reference to FIGS. **14** to **17**.

[0185] First, in this embodiment, a substrate 300 is used, which is made of glass such as barium borosilicate glass or alumino borosilicate glass, typified by #7059 glass or #1737 glass of Corning Inc. There is no limitation on the substrate 300 as long as a substrate having a light transmitting property is used, and a quartz substrate may also be used. In addition, a plastic substrate having heat resistance to a treatment temperature of this embodiment may also be used.

[0186] Then, a base film 301 formed of an insulating film such as a silicon oxide film, a silicon nitride film or a silicon oxynitride film is formed on the substrate 300. In this embodiment, a two-layer structure is used for the base film 301. However, a single layer film or a lamination structure consisting of two or more layers of the insulating film may also be used. As a first layer of the base film 301, a silicon oxynitride film 301a is formed with a thickness of 10 to 200 nm (preferably 50 to 100 nm) using SiH<sub>4</sub>, NH<sub>3</sub>, and N<sub>2</sub>O as reaction gases by a plasma CVD method. In this embodiment, the silicon oxynitride film 301a (composition ratio Si=32%, O=27%, N=24% and H=17%) having a film thickness of 50 nm is formed. Then, as a second layer of the base film 301, a silicon oxynitride film 301b is formed so as to be laminated on the first layer with a thickness of 50 to 200 nm (preferably 100 to 150 nm) using SiH<sub>4</sub> and N<sub>2</sub>O as reaction gases by the plasma CVD method. In this embodiment, the silicon oxynitride film 301b (composition ratio Si=32%, O=59%, N=7% and H=2%) having a film thickness of 100 nm is formed.

[0187] Subsequently, semiconductor layers 302 to 305 are formed on the base film. The semiconductor layers 302 to 305 are formed such that a semiconductor film having an amorphous structure is formed by a known method (a sputtering method, an LPCVD method, a plasma CVD method or the like), and is subjected to a known crystallization process (a laser crystallization method, a thermal crystallization method, a thermal crystallization method using a catalyst such as nickel, or the like) to obtain a crystalline semiconductor film, and the crystalline semiconductor film is pat-

terned into desired shapes. The semiconductor layers 302 to 305 are formed with a thickness of 25 to 80 nm (preferably 30 to 60 nm). The material of the crystalline semiconductor film is not particularly limited, but it is preferable to fowl the film using silicon, a silicon germanium (Si<sub>x</sub> Ge<sub>1-x</sub>(X=0.0001 to 0.02)) alloy, or the like. In this embodiment, an amorphous silicon film of 55 nm thickness is formed by a plasma CVD method, and then, a nickel-containing solution is held on the amorphous silicon film. A dehydrogenation process of the amorphous silicon film is performed (at 500° C. for 1 hour), and thereafter a thermal crystallization process is performed (at 550° C. for 4 hours) thereto. Further, to improve the crystallinity, a laser annealing process is performed to form the crystalline silicon film. Then, this crystalline silicon film is subjected to a patterning process using a photolithography method to obtain the semiconductor layers 302 to 305.

[0188] Further, after the formation of the semiconductor layers 302 to 305, a minute amount of impurity element (boron or phosphorus) may be doped to control a threshold value of the TFT.

[0189] Besides, in the case where the crystalline semiconductor film is manufactured by the laser crystallization method, a pulse oscillation type or continuous emission type excimer laser, YAG laser, or YVO4 laser may be used. In the case where those lasers are used, it is appropriate to use a method in which laser light radiated from a laser oscillator is condensed into a linear shape by an optical system, and is irradiated to the semiconductor film. Although the conditions of crystallization should be properly selected by an operator, in the case where the excimer laser is used, a pulse oscillation frequency is set to 30 Hz, and a laser energy density is set to 100 to 400 mJ/cm<sup>2</sup> (typically 200 to 300 mJ/cm<sup>2</sup>). In the case where the YAG laser is used, it is appropriate to set a pulse oscillation frequency as 1 to 10 Hz using the second harmonic, and to set a laser energy density to 300 to 600 mJ/cm<sup>2</sup> (typically, 350 to 500 mJ/cm<sup>2</sup>). Then, laser light condensed into a linear shape with a width of 100 to 1000 µm, for example, 400 is irradiated to the whole surface of the substrate, and an overlapping ratio (overlap ratio) of the linear laser light at this time may be set to 50 to 90%.

[0190] A gate insulating film 306 is then formed for covering the semiconductor layers 302 to 305. The gate insulating film 306 is formed of an insulating film containing silicon with a thickness of 40 to 150 nm by a plasma CVD or sputtering method. In this embodiment, the gate insulating film 306 is formed of a silicon oxynitride film with a thickness of 110 nm by the plasma CVD method (composition ratio Si=32%, O=59%, N=7%, and H=2%). Of course, the gate insulating film is not limited to the silicon oxynitride film, and other insulating films containing silicon may be used with a single layer or a lamination structure.

**[0191]** Besides, when a silicon oxide film is used, it can be formed such that TEOS (tetraethyl orthosilicate) and  $\rm O_2$  are mixed by the plasma CVD method with a reaction pressure of 40 Pa and a substrate temperature of 300 to 400° C., and discharged at a high frequency (13.56 MHz) power density of 0.5 to 0:8 W/cm². The silicon oxide film thus manufactured can obtain satisfactory characteristics as the gate insulating film by subsequent thermal annealing at 400 to 500° C.

[0192] Then, as shown in FIG. 14A, a first conductive film 307 of 20 to 100 nm thickness and a second conductive film 308 of 100 to 400 nm thickness are formed into lamination on the gate insulating film 306. In this embodiment, the first conductive film 307 made of a TaN film with a thickness of 30

nm and the second conductive film 308 made of a W film with a thickness of 370 nm are formed into lamination. The TaN film is formed by sputtering with a Ta target under a nitrogen containing atmosphere. Besides, the W film is formed by sputtering with a W target. The W film may also be formed by a thermal CVD method using tungsten hexafluoride (WF<sub>6</sub>). Whichever method is used, it is necessary to make the material have low resistance for use as a gate electrode, and it is preferred that the resistivity of the W film is set to  $20\,\mu\Omega$ cm or less. It is possible to make the W film have low resistance by making the crystal grains large. However, in the case where many impurity elements such as oxygen are contained within the W film, crystallization is inhibited and the resistance becomes higher. Therefore, in this embodiment, the W film is formed by sputtering using a W target having a high purity of 99.9999%, and also by taking sufficient consideration so as to prevent impurities within the gas phase from mixing therein during the film formation, and thus, a resistivity of 9 to 20  $u\Omega$ cm can be realized.

[0193] Note that, in this embodiment, the first conductive film 307 is made of TaN, and the second conductive film 308 is made of W, but the material is not particularly limited thereto, and either film may be formed from an element selected from the group consisting of Ta, W, Ti, Mo, Al, Cu, Cr, and Nd or an alloy material or a compound material containing the above element as its main constituent. Besides, a semiconductor film typified by a polycrystalline silicon film doped with an impurity element such as phosphorus may be used. An alloy made of Ag, Pd, and Cu may also be used. Further, any combination may be employed such as a combination in which the first conductive film is formed of a tantalum (Ta) film and the second conductive film is formed of a W film, a combination in which the first conductive film is formed of a titanium nitride (TiN) film and the second conductive film is formed of a W film, a combination in which the first conductive film is formed of a tantalum nitride (TaN) film and the second conductive film is formed of an Al film, or a combination in which the first conductive film is formed of a tantalum nitride (TaN) film and the second conductive film is formed of a Cu film.

[0194] Next, as shown in FIG. 14B, masks 309 to 313 made of resist are formed by using a photolithography method, and a first etching process for forming electrodes and wirings is carried out. In the first etching process, first and second etching conditions are used. In this embodiment, as the first etching condition, an ICP (inductively coupled plasma) etching method is used, in which CF<sub>4</sub>, Cl<sub>2</sub>, and O<sub>2</sub> are used as etching gases, a gas flow rate is set to 25/25/10 sccm, and an RF (13.56 MHz) power of 500 W is applied to a coil shape electrode under a pressure of 1 Pa to generate plasma. Thus, the etching is performed. A dry etching device using ICP (Model E645-ICP) manufactured by Matsushita Electric Industrial Co. is used here. A 150 W RF (13.56 MHz) power is also applied to the substrate side (sample stage), thereby substantially applying a negative self-bias voltage. The W film is etched under the first etching condition, and the end portion of the first conductive layer is formed into a tapered shape. In the first etching condition, the etching rate for W is 200.39 nm/min, the etching rate for TaN is 80.32 nm/min, and the selectivity of W to TaN is about 2.5. Further, the taper angle of W is about 26° under the first etching condition.

[0195] Thereafter, as shown in FIG. 14B, the etching condition is changed into the second etching condition without removing the masks 309 to 313 made of resist, and the etching

is performed for about 30 seconds, in which  $\mathrm{CF_4}$  and  $\mathrm{Cl}$ , are used as the etching gases, a gas flow rate is set to 30/30 sccm, and an RF (13.56 MHz) power of 500 W is applied to a coil shape electrode under a pressure of 1 Pa to generate plasma. An RF (13.56 MHz) power of 20 W is also applied to the substrate side (sample stage), and a substantially negative self-bias voltage is applied thereto. In the second etching condition in which  $\mathrm{CF_4}$  and  $\mathrm{Cl}$ , are mixed, the W film and the TaN film are etched to the same degree. In the second etching condition, the etching rate for W is 58.97 nm/min, and the etching rate for TaN is 66.43 nm/min. Note that, in order to perform the etching without leaving any residue on the gate insulating film, it is appropriate that an etching time is increased by approximately 10 to 20%.

[0196] In the above first etching process, by making the shapes of the masks formed of resist suitable, end portions of the first conductive layer and the second conductive layer become tapered shape by the effect of the bias voltage applied to the substrate side. The angle of the taper portion may be 15 to 45°. In this way, first shape conductive layers 314 to 318 consisting of the first conductive layer and the second conductive layer (first conductive layers 314a to 318a and second conductive layers 314b to 318b) are formed by the first etching process. Reference numeral 319 indicates a gate insulating film, and the regions not covered with the first shape conductive layers 314 to 318 are made thinner by approximately 20 to 50 nm by etching.

[0197] Then, a first doping process is performed to add an impurity element imparting n-type conductivity to the semiconductor layer without removing the masks made of resist (FIG. 14B). Doping may be carried out by an ion doping method or an ion injecting method. The condition of the ion doping method is that a dosage is  $1 \times 10^{13}$  to  $5 \times 10^{15}$  atoms/ cm<sup>2</sup>, and an acceleration voltage is 60 to 100 keV. In this embodiment, the dosage is 1.5×10<sup>15</sup> atoms/cm<sup>2</sup> and the acceleration voltage is 80 keV. As the impurity element imparting n-type conductivity, an element belonging to group 15 of the periodic table, typically phosphorus (P) or arsenic (As) is used, but phosphorus (P) is used here. In this case, the conductive layers 314 to 318 become masks for the impurity element imparting n-type conductivity, and high concentration impurity regions 320 to 323 are formed in a self-aligning manner. The impurity element imparting n-type conductivity in a concentration range of  $1 \times 10^{20}$  to  $1 \times 10^{21}$  atoms/cm<sup>3</sup> is added to the high concentration impurity regions 320 to 323. [0198] Thereafter, as shown in FIG. 14C, a second etching process is performed without removing the masks made of resist. Here, a gas mixture of CF<sub>4</sub>, Cl<sub>2</sub> and O<sub>2</sub> is used as an etching gas, the gas flow rate is set to 20/20/20 sccm, and a 500 W RF (13.56 MHz) power is applied to a coil shape electrode under a pressure of 1 Pa to generate plasma, thereby performing etching. A 20 W RF (13.56 MHz) power is also applied to the substrate side (sample stage), thereby substantially applying a negative self-bias voltage. In the second etching process, the etching rate for W is 124.62 nm/min, the etching rate for TaN is 20.67 nm/min, and the selectivity of W to TaN is 6.05. Accordingly, the W film is selectively etched. The taper angle of W is 70° by the second etching process. Second conductive layers 324b to 328b are formed by the second etching process. On the other hand, the first conductive layers 314a to 318a are hardly etched, and first conductive layers 324a to 328a are formed.

[0199] Next, as shown in FIG. 15A, a second doping process is performed. The second conductive layers 324b to 328b

are used as masks for an impurity element, and doping is performed such that the impurity element is added to the semiconductor layer below the tapered portions of the first conductive layers. In this embodiment, phosphorus (P) is used as the impurity element, and plasma doping is performed with a dosage of  $1.5 \times 10^{14}$  atoms/cm<sup>2</sup>, a current density of 0.5μA, and an acceleration voltage of 90 keV. Thus, low concentration impurity regions 329 to 333, which overlap with the first conductive layers, are formed in self-aligning manner. The concentration of phosphorus (P) added to the low concentration impurity regions 329 to 333 is  $1\times10^{17}$  to  $5\times10^{18}$ atoms/cm<sup>3</sup>, and has a gentle concentration gradient in accordance with the film thickness of the tapered portions of the first conductive layers. Note that in the semiconductor layers that overlap with the tapered portions of the first conductive layers, the concentration of the impurity element slightly falls from the end portions of the tapered portions of the first conductive layers toward the inner portions, but the concentration keeps almost the same level. Further, an impurity element is added to the high concentration impurity regions 333 to 337 to form high concentration impurity regions 333 to 337.

[0200] Thereafter, as shown in FIG. 15B, after the masks made of resist are removed, a third etching process is performed using a photolithography method. The tapered portions of the first conductive layers are partially etched so as to have shapes overlapping the second conductive layers in the third etching process. Incidentally, as shown in FIG. 15B, masks made of resist (338 and 339) are formed in the regions where the third etching process is not conducted.

**[0201]** The etching condition in the third etching process is that  $\rm Cl_2$  and  $\rm SF_6$  are used as etching gases, the gas flow rate is set to 10/50 sccm, and the ICP etching method is used as in the first and second etching processes. Note that, in the third etching process, the etching rate for TaN is 111.2 nm/min, and the etching rate for the gate insulating film is 12.8 nm/min.

[0202] In this embodiment, a 500 W RF (13.56 MHz) pow er is applied to a coil shape electrode under a pressure of 1.3 Pa to generate plasma, thereby performing etching. A 10 W RF (13.56 MHz) power is also applied to the substrate side (sample stage), thereby substantially applying a negative selfbias voltage. Thus, first conductive layers 340a to 342a are

[0203] Impurity regions (LDD regions) 343 to 345, which do not overlap the first conductive layers 340a to 342a, are formed by the third etching process. Note that impurity regions (GOLD regions) 346 and 347 remains overlapping the first conductive layers 324a and 326a.

[0204] Further, the electrode constituted of the first conductive layer 324a and the second conductive layer 324b finally becomes the gate electrode of the n-channel TFT of the driver circuit, and the electrode constituted of the first conductive layer 340a and a second conductive layer 340b finally becomes the gate electrode of the p-channel TFT of the driver circuit.

[0205] Similarly, the electrode constituted of the first conductive layer 341a and a second conductive layer 341b finally becomes the gate electrode of the n-channel of the pixel portion, and the electrode constituted of the first conductive layer 342a and a second conductive layer 342b finally becomes the gate electrode of the p-channel TFT of the pixel portion. Further, the electrode constituted of the first conduc-

tive layer **326***a* and the second conductive layer **326***b* finally becomes one of electrodes of a capacitor (storage capacitor) of the pixel portion.

[0206] In this way, in this embodiment, the impurity regions (LDD regions) 343 to 345 that do not overlap the first conductive layers 340a to 342a and the impurity regions (GOLD regions) 346 and 347 that overlap the first conductive layers 324a and 326a can be simultaneously formed. Thus, different impurity regions can be formed in accordance with the TFT characteristics.

[0207] Next, the gate insulating film 319 is subjected to an etching process. In this etching process, CHF $_3$  is used as an etching gas, and a reactive ion etching method (RIE method) is used. In this embodiment, a third etching process is conducted with a chamber pressure of 6.7 Pa, RF power of 800 W, and a gas flow rate of CHF $_3$  of 35 sccm.

[0208] Thus, parts of the high concentration impurity regions 333 to 337 are exposed, and insulating films 356a to 356e are formed.

[0209] Subsequently, after the masks made of resist are removed, masks 348 and 349 made of resist are newly formed to thereby perform a third doping process. By this third doping process, impurity regions 350 to 355 added with an impurity element imparting conductivity (p-type) opposite to the above conductivity (n-type) are formed in the semiconductor layers that become active layers of the p-channel TFT (FIG. 15C). The first conductive layers 340a, 326a, and 342a are used as masks for the impurity element, and the impurity element imparting p-type conductivity is added to form the impurity regions in a self-aligning manner.

[0210] In this embodiment, the impurity regions 350 to 355 are formed by an ion doping method using diborane ( $\rm B_2H_6$ ). Note that, in the third doping process, the semiconductor layers forming the n-channel TFTs are covered with the masks 348 and 349 made of resist. The impurity regions 350 to 355 are respectively added with phosphorous at different concentrations by the first doping process and the second doping process. In any of the regions, the doping process is conducted such that the concentration of the impurity element imparting p-type conductivity becomes  $2\times10^{20}$  to  $2\times10^{21}$  atoms/cm³. Thus, the impurity regions function as source and drain regions of the p-channel TFT, and therefore, no problem occurs.

[0211] Through the above-described processes, the impurity regions are formed in the respective semiconductor layers.

[0212] Note that, in this embodiment, a method of conducting doping of the impurities (boron) after etching the gate insulating film is shown, but doping of the impurities may be conducted before etching the gate insulating film.

[0213] Subsequently, the masks 348 and 349 made of resist are removed, and as shown in FIG. 16A, a first interlayer insulating film 357 is formed. As the first interlayer insulating film 357, an insulating film containing silicon is formed with a thickness of 100 to 200 nm by a plasma CVD method or a sputtering method. In this embodiment, a silicon oxynitride film of 150 nm thickness is formed by the plasma CVD method. Of course, the first interlayer insulating film 357 is not limited to the silicon oxynitride film, and other insulating films containing silicon may be used in a single layer or a lamination structure.

[0214] Then, a process of activating the impurity element added to the semiconductor layers is performed. This activation process is performed by a thermal annealing method

using an annealing furnace. The thermal annealing method may be performed in a nitrogen atmosphere with an oxygen concentration of 1 ppm or less, preferably 0.1 ppm or less and at 400 to 700° C., typically 500 to 550° C. In this embodiment, the activation process is conducted by a heat treatment for 4 hours at 550° C. Note that, in addition to the thermal annealing method, a laser annealing method or a rapid thermal annealing method (RTA method) can be applied.

[0215] Note that, in this embodiment, with the activation process, nickel used as a catalyst in crystallization is gettered to the impurity regions containing phosphorous at high concentration, and the nickel concentration in the semiconductor layer that becomes a channel forming region is mainly reduced. The TFT thus manufactured having the channel forming region has the lowered off current value and good crystallinity to obtain a high electric field effect mobility. Thus, the satisfactory characteristics can be attained.

[0216] Further, the activation process may be conducted before the formation of the first interlayer insulating film. Incidentally, in the case where the used wiring material is weak to heat, the activation process is preferably conducted after the formation of the interlayer insulating film (insulating film containing silicon as its main constituent, for example, silicon nitride film) in order to protect wirings and the like as in this embodiment.

[0217] Furthermore, after the activation process and the doping process, the first interlayer insulating film may be formed.

[0218] Moreover, a heat treatment is carried out at 300 to 550° C. for 1 to 12 hours in an atmosphere containing hydrogen of 3 to 100% to perform a process of hydrogenating the semiconductor layers. In this embodiment, the heat treatment is conducted at 410° C. for 1 hour in a nitrogen atmosphere containing hydrogen of approximately 3%. This is a process of terminating dangling bonds in the semiconductor layer by hydrogen included in the interlayer insulating film. As another means for hydrogenation, plasma hydrogenation (using hydrogen excited by plasma) may be performed.

[0219] In addition, in the case where the laser annealing method is used as the activation process, after the hydrogenation process, laser light emitted from an excimer laser, a YAG laser or the like is desirably irradiated.